Adobe Reader 64 Bit Fixes A Draft

Microprocessor Report Archive. Embedded Skylake Speeds Networking. Intel Unveils New Xeon Processors and South- Bridge Accelerators. Bronze, Silver, Gold, Platinum: four color- coded product tiers familiar to anyone who has purchased an Obamacare health- insurance plan.

InformationWeek.com: News, analysis and research for business technology professionals, plus peer-to-peer knowledge sharing. Engage with our community. A noisy cheer went up from the crowd of hackers clustered around the voting machine tucked into the back corner of a casino conference room—they’d just managed to. Free Download Software Sql Injection Attacks more. Daily paper. Local, state, and wire news and commentary. Photo galleries, business and obituaries.

Most major publishers use Adobe Digital Editions (ADE) to proof-read their books. Download this free eReader to experience your books in the most optimum format. Here's an index of Tom's articles in Microprocessor Report. All articles are online in HTML and PDF formats for paid subscribers. Ever notice how Christopher Nolan’s movies (Interstellar, Inception, The Prestige) feel like an anxiety attack? Well, maybe that’s overstating things a bit. Description. Since the restriction of the Unicode code-space to 21-bit values in 2003, UTF-8 is defined to encode code points in one to four bytes, depending on the. This update includes support for Mac OSX 10.11, Rulers and Guides, Roundtripping with Adobe Creative Cloud 2015 and other bug fixes. For detailed information on the.

They're also Intel's new tiers for Xeon Scalable processors. These chips supersede the Xeon E5v. Broadwell- EP core.

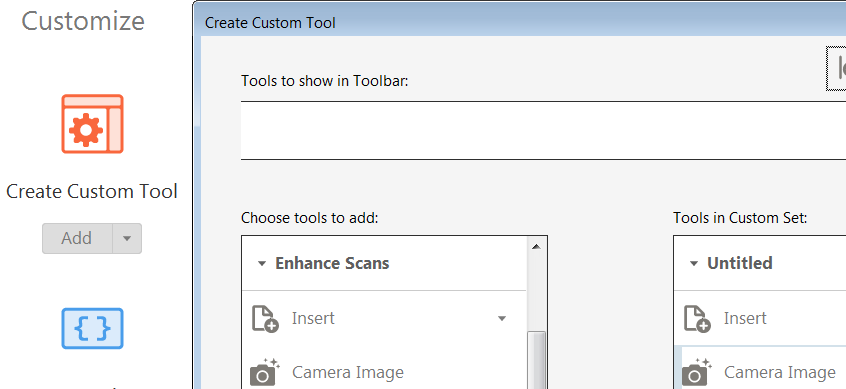

View and Download Adobe Photoshop CS6 user manual online. Photoshop CS6 Software pdf manual download.

Like the insurance policies, the lower tiers (Bronze and Silver) cost less but offer fewer benefits than the higher tiers (Gold and Platinum). The 1. 6 new Xeon embedded processors derive from the new Skylake- SP server processors but have extended availability. Had Intel kept its usual branding, they would be Xeon E5v. These chips have an improved CPU microarchitecture that executes about 5% more instructions per clock cycle than Broadwell. In addition, they exceed their Xeon E5v.

PCI Express lanes, multisocket connectivity, power consumption, and list price. One obsession is removing all blemishes from the front surface—including the tiny holes, or .

The biggest aperture by far is the elongated speaker slot—but it's necessary until the last few holdouts finally stop using their phones to make phone calls. The next- largest aperture is for the selfie camera's lens, but it's required until narcissism becomes unfashionable. So, by process of elimination, the apertures for the front- facing sensors are the best candidates for elimination. That's why AMS, the industry's largest supplier of light sensors, has invented new modules that can hide behind an inked screen bezel of any color without sacrificing performance. The industry consortium has introduced its first Io. T- Communications suite, which measures the power consumption of a typical Io. T client that transfers data using Bluetooth Low Energy (BLE).

By far the most complex suite EEMBC has developed in its 2. Io. TMark- BLE is available for order now by members and nonmembers. It's scheduled to ship in June. Instead of measuring power, Io. TMark- BLE actually measures energy consumption—power over time.

The distinction is important because battery life depends on the total current a microcontroller draws to perform a particular task, regardless of its throughput performance. Thus, Io. TMark- BLE measures total energy consumption during several sleep- wake- sleep cycles for a typical task. Along with its enhanced packet acceleration, the new LA1. Wi- Fi routers, 5. G cellular radios, and mixed wired/wireless applications, such as fixed- wireless nodes in neighborhood fiber- optic networks.

Designed primarily for residential and small- business Internet gateways, enterprise access points, and fixed- wireless applications, the LA1. Both models have ARM Cortex- A5. CPUs, and their target clock frequency is 1. Although NXP is withholding many specifications for now, the most important new features are a programmable vector engine for Layer 1 processing, enhanced accelerators for Layer 2 processing, and an integrated RFIC interface with analog- to- digital and digital- to- analog converters (ADCs/DACs).

Sampling now, they extend the AM5. Like other AM5. 7x processors, they integrate an ARM Cortex- A1. CPU with two Cortex- M4 controller cores, a C6.

DSP, and TI's own programmable controller cores. Several economy measures suit the AM5. AM5. 70. 8 to low- end applications, such as drones, remote sensors, and motors. Compared with the smallest previous AM5. Macromedia Studio Mx 2004 All In One Cd Key here. Cortex- A1. 5 CPU by 3.

GHz. The C6. 6x DSP core runs at 7. MHz as usual, but some models have a 5. MHz CPU and DSP. No competing products can match their features for signal processing, floating- point throughput, and real- time control.

Four chips in the new i. MX8. M- series have ARMv. CPUs and enough additional processing power for most digital- media applications. The superset design is the i. MX8. M Quad, which has four 6.

Cortex- A5. 3 CPUs, one 3. Cortex- M4. F coprocessor, a Veri. Silicon GPU, a high- performance video engine, a multichannel audio engine, and dual camera interfaces. The i. MX8. M Quad.

Lite, Dual, and Solo models are subsets of this design. All four chips are scheduled to sample in 1. Q1. 7 and reach volume production in 4.

Q1. 7. The new i. MX8. M processors comprise the media- centric branch of the i. MX8 family, which has now more than doubled in size.

The first three chips in this family—the i. MX8 Quad. Max, Quad.

Plus, and Quad—are even more powerful. The i. MX8 superset design is the Quad. Max, which more than doubles the processing power by adding two Cortex- A7. CPUs to the i. MX8. M configuration. NXP expects to sample the i. MX8- series by 2.

Q1. 7, with production sometime in 2. H1. 8. At least that's how it seemed in 2. Companies continued to devour one another, further consolidating an embedded- processor market dominated by a dwindling number of major players. Although the acquisitions are creating larger companies with more resources, some products and roadmaps are falling victim to cost cutting. Looking forward, we expect 2. ARM will gain momentum without slowing Intel's. Qualcomm will be the rising star after absorbing NXP, and Broadcom and Cavium will battle for third place.

Code- named Apollo Lake, these 1. Celeron and Pentium products for entry- level PCs, three Atom E3. A3. 90. 0 embedded models for automotive. Their integrated GPUs support 4.

K- resolution graphics and up to three displays. The embedded models target Io. T gateways, industrial automation, vehicle infotainment systems, automotive instrument panels, driver- assistance systems, retail kiosks, and other high- end applications.

Apollo Lake supersedes the three- year- old Bay Trail. The PC versions are shipping now, and the embedded models are scheduled for volume production next quarter. The new Core. Link CMN- 6. CPUs in a memory- coherent mesh network while boosting throughput by up to 5x over ARM's existing interconnects—making a play for server processors.

And the new Core. Link DMC- 6. 20 is an enterprise- class memory controller that slashes the DRAM latency by up to 5. Preliminary RTL for both products is available now as licensable intellectual property (IP), and we expect production RTL to arrive later this year. The new Cortex- R5.

ARMv. 8- R design that supports hypervisors by adding another privilege level and a second memory- protection unit. It can simultaneously run multiple real- time operating systems in virtual sandboxes, isolating critical tasks from others. It also boosts performance relative to the existing Cortex- R5, offering superior throughput, optional Neon SIMD extensions, faster context switching, and faster interrupt handling. Long awaited, Cortex- R5. ARMv. 8- R instruction- set architecture (ISA) announced three years ago. The new core omits the 6. ARMv. 8 and implements only a subset of the cryptographic instructions.

But it's backward compatible with the 3. ARMv. 7- R architecture, including the compressed Thumb instructions. The 6. 4- core FT- 2. Mars, targets a maximum CPU frequency of 2.

GHz and will initially sell to domestic customers. The company has also disclosed the first details of two smaller processors: the 1. FT- 1. 50. 0A/1. 6 and 4- core FT- 1.

A/4. These 1. 5. GHz chips employ a slightly less muscular ARMv. CPU core that's more power efficient but is otherwise similar to the bigger processor's core. Phytium says both chips have been in production since last year. The 1. 6- core model is designed for web servers, cloud computing, transaction processing, and network switching. The quad- core model is designed for small servers, desktops, laptops, and embedded systems.

Phytium showed the FT- 2. U server at the recent Hot Chips conference in Silicon Valley. It was running cloud- computing software from Tianjin Kylin—an incorporated spinoff from China's National University of Defense Technology, which built the world's fastest supercomputers, Tianhe- 1 and Tianhe- 2, in 2. Compared with earlier ARC products, the new ARC SEM1.